南京中电熊猫液晶显示科技有限公司 江苏 南京 210046

摘要:以TFT工艺为基础的器件,主要的材料包括绝缘层(SiNx)、非晶硅半导体层(a-Si)和电极层材料。其中,绝缘层和非晶硅层需要通过CVD成膜制备。在所有CVD成膜技术中,PECVD可以起到明显的增强效果,该种技术的能量来自等离子体(Plasma),反应气体的活性增加,保证薄膜在积淀之后可以更加均一,同时具有良好的覆盖率。本文主要分析了工艺参数对PECVD氮化硅成膜效率的影响,在实验的过程中对以射频功率为代表的几个参数进行调整,最后得出相关的实验结论。

关键词:TFT工艺;CVD成膜;成膜速率

Abstract: For devices based on TFT technology, the main materials include insulating layer (SiNx), amorphous silicon semiconductor layer (a-Si) and electrode layer materials. Among them, the insulating layer and the amorphous silicon layer need to be prepared by CVD film formation. Among all CVD film forming technologies, PECVD can play an obvious enhancement effect. The energy of this technology comes from plasma (Plasma), and the activity of the reactive gas is increased to ensure that the film can be more uniform after deposition and has a good coverage rate. . This article mainly analyzes the influence of process parameters on the efficiency of PECVD silicon nitride film formation, and adjusts several parameters represented by RF power during the experiment, and finally draws relevant experimental conclusions.

Keywords: TFT process; CVD film formation; film formation rate

前言:

目前,TFT-LCD工艺技术与其他材料技术发展的速度愈发加快,这直接导致了这一领域市场竞争的白热化,由于技术进步带来的成本不断压缩,但是对于产品质量的要求却逐渐提高。在制备TFT的过程中,TFT的性能将直接受到非金属膜质的影响,因此,在不断完善TFT工艺的过程中,必须将非金属膜层的成膜摆在突出位置上,予以高度的重视。在CVD成膜的实际生产过程中,必须兼顾生产的产能和成膜的质量,为此需要对工艺参数进行调整,而这项工作的完成需要控制膜质的成膜速率,鉴于此,TFT产品在成膜的过程中必须重视CVD单模成膜的影响。基于此,本文在研究成膜速率的过程中,以非金属的单膜作为着手点,调整工艺参数。

实验设计

本次的实验主要研究的内容是利用TFT技术对PECVD氮化硅成膜处理,分析各个工艺参数对成膜速率不同的影响,因此,在实验设计的过程中要充分认识到这一点。在实验过程中,使用等离子体化学气相沉积设备制备氮化硅(SiNx)在本次的实验中,需要使用到多种气体,包括SiH4、NH3和N2等。在实验中,使用这些气体的目的在于在CVD成膜之前的一段时间内完成必要的清洁工作。在本次的实验中,CVD成膜的温度需要设定在340℃~380℃。同时,为了衡量成膜速率这一实验中最关键的数据,在本次的实验中还需要利用到专业的设备——椭偏光仪器,该种仪器可以有效对实验中各个工艺参数对成膜速率的影响进行衡量。除此之外,实验中样品成膜需要使用到的玻璃基板,在本次实验中,玻璃基板的规格选为1800mm×1500mm,为了不对成膜过程产生任何影响,在成膜之前,必须使用清洗步骤除去异物Particles、EUV光照除去有机物完成清洁工作。

本文采用AKT-25K型设备,使用的气体为SiH4(纯度为99.9999%)、N2(纯度为99.999%)和NH3(纯度为99.9999%)。本文采用等离子体增强化学气象沉积 (PECVD) 法在1800mm×1500mm玻璃基板上沉积一层250~355nm 的氮化硅(SiNx)薄膜。

在PECVD氮化硅成膜的过程中,存在众多的工艺参数,但是能够对成膜的速率产生影响的关键参数仅为几种,一是射频功率(Power)、二是成膜压强(Pressure)、三是电极之间的距离(Spacing)、四是SiH4流量。为了方便实验的进行,也为了清晰观察这四个工艺参数对于成膜速率的影响,在本次的实验中一共设计了四个变量,其中三个为固定变量,一个变量用于研究。

实验结果分析

2.1成膜速率受射频功率的影响

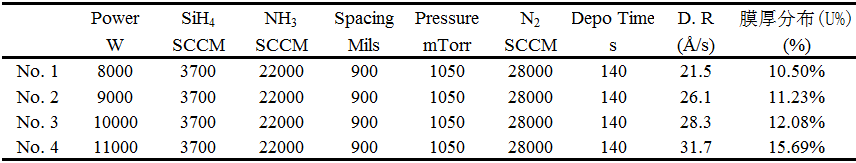

在实验的第一个环节中,分析了射频功率对于CVD成膜效率的影响,本次实验中的射频功率选定在4水平,并且遵循一个重要前提——4次成膜的条件,除了成膜射频功率不同外,其它成膜工艺参数都相同,避免了其它工艺参数对实验产生的负面影响,实验条件和实验结果,如表1。

表1射频功率对氮化硅薄膜成膜速率和膜厚分布的影响

Tab.1 Effect of RF power on the formation rate and distribution of Silicon nitride thin film

本次实验的结果,如表1。在实验中,射频功率逐渐增大的过程中,氮化硅成膜的速度和效率在不断加快,两者之间成明显的正比关系。在实验中,当射频功率在不断加大的过程中,在氮化硅腔室之内,成膜的气体受到功率巨大的能量,腔室内各种气体的分解速度加快,进而导致等离子体的密度逐渐增加,在实验中,玻璃基板的表面上吸附的活性原子和离子逐渐增多,这就是射频功率加快,成膜速率提高的根本原因[1]。但是,这只是实验中的表现,在现实的生产工作中,关注的主要指标不是较高的成膜速率,这是因为一旦成膜速率过高,形成的膜质反而会越差,这就是所谓的“欲速则不达”。

2.2成膜速率受成膜压强的影响

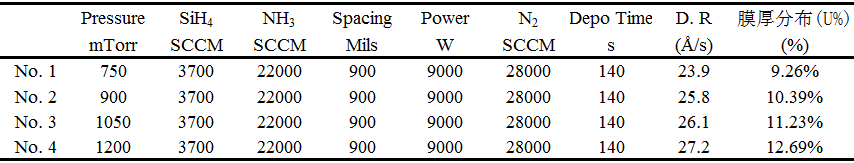

在实验的第二个环节中,分析了成膜压强对CVD成膜速率的影响,实验中将成膜压强选定在4水平,为了不影响实验的结果,除了成膜压强不同外,其它成膜工艺参数都相同,实验条件和实验结果,如表2。

表2 成膜压力对氮化硅薄膜成膜速率和膜厚分布的影响

Tab.2 Effect of pressure on the formation rate and distribution of Silicon nitride thin film

根据实验的结果可知,成膜的速率与成膜的压强之间呈正比。在用于反应实验的腔室之内,成膜压强的持续增大将会导致各种反应物之间的反应频率加快,在这一过程中,等离子体的平均自由程将会降低,这就直接导致了单位时间内,玻璃基板的表面增加了更多的粒子,导致成膜的速率显著增加[2]。

2.3成膜速率受电极间距的影响

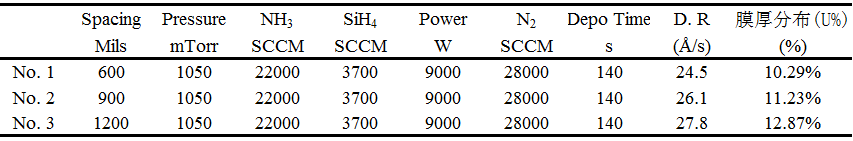

在实验的第三个环节中,分析了电极之间的距离对CVD成膜速率的影响,在本环节的实验过程中,将电极之间的距离设定为3水平,同样为了避免成膜速率的实验结果受到影响,实验中将3次成膜的工艺参数除了电极间距不同外,其它工艺参数都相同,实验条件和实验结果,如表3。

表3 电极间距对氮化硅薄膜成膜速率和膜厚分布的影响

Tab.3 Effect of spacing on the formation rate and distribution of Silicon nitride thin film

在本环节的实验中,电极之间的距离逐渐增大,成膜的速率也相对加快,这意味着电极之间距离与成膜速率之间呈正比。在实验中用于反应的腔室体积直接受电极之间距离的影响,同时,在实验的过程中,等离子体的密度也会受到电极之间距离的影响,如果电极之间的距离过小,强气流会在反应物中等离子体没有及时反应的情况下将其直接带走。如果电极之间的距离过大,成膜的质量会显著降低[3]。

2.4成膜速率受SiH4流量的影响

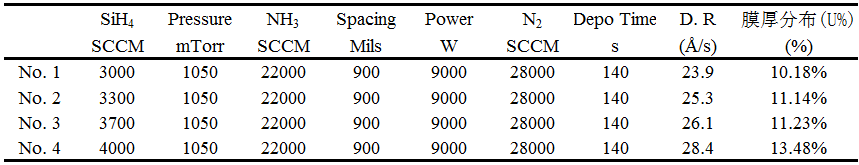

在实验的第四个环节中,探究成膜速率受SiH4流量的影响。实验结果和实验条件,如表4。

表4 SiH4流量对氮化硅薄膜成膜速率和膜厚分布的影响

Tab.4 Effect of SiH4 gas flow on the formation rate and distribution of Silicon nitride thin film

根据相应的研究成果可知,CVD成膜的化学成分直接受到SiH4的影响。流量增大,则相应的气体流量也会增大,单位体积内的等离子体密度也会增加。但是流量一旦过大,氮化硅膜中的Si含量提升,会影响膜的折射率,氮化硅的电学性能会因此降低。

2.5不同工艺参数的变化对成膜速率的影响程度

将上述四个环节中,不同的工艺参数对CVD成膜速率的影响情况进行汇总,将其中对成膜速率影响最大的工艺参数挑选出来,具体的结果,详见表1、2、3、4和5。在一定的范围之内,CVD成膜的速率受射频功率的影响最大,在实验中,射频功率越大,成膜的速率提升越快,这与其他三种工艺参数之间产生了明显得差异

[4]。

结束语

成膜速率受到不同工艺参数的影响,产生不同的表现。在本文实验的四种工艺参数中,对成膜速率影响最大的是射频功率,其他三种工艺参数也会对成膜的速率产生影响,只不过影响的程度难以与射频功率相比。因此,为了生产出性能更优的产品,需要选择最合适的工艺参数,控制非金属的膜质,进而完成对成膜速率的控制。

参考文献:

[1]杨国波,赵文星,孙泉钦,等.应用于AMOLED薄膜封装的高应力氮化硅工艺探讨[J].电子世界,2020,No.591(09):44-45+48.

[2]李婷婷.富硅—氮化硅薄膜及其硅量子点的制备及结构研究[D].内蒙古师范大学,2019.

[3]李攀,张倩,夏金松,等.PECVD氮化硅薄膜性质及工艺研究[J].光学仪器,2019,v.41;No.229(03):84-89.

[4]付学成, 权雪玲, 乌李瑛,等. ICP-CVD设备低温制备低应力氮化硅薄膜工艺的探索[J]. 真空科学与技术学报, 2019(10):896-900.